- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT5T929-30NLGI (IDT, Integrated Device Technology Inc)IC CLOCK GENERATOR PREC 28VFQFPN

1

INDUSTRIALTEMPERATURERANGE

IDT5T929

PRECISIONCLOCKGENERATOROC-48APPLICATIONS

2013

Integrated Device Technology, Inc.

DSC 6400/17

c

IDT5T929

INDUSTRIAL TEMPERATURE RANGE

PRECISION CLOCK GENERATOR

OC-48 APPLICATIONS

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

Input frequency:

- ForSONETnon-FEC:19.44MHz,38.88MHz,77.76MHz,155.52MHz,

311.04MHz, or 622.08MHz

- For SONET FEC: 20.83MHz, 41.66MHz, 83.31MHz, 166.63MHz,

333.26MHz, or 666.52MHz

- For 10GE copper: 19.53MHz, 39.06MHz, 78.125MHz, 156.25MHz,

312.5MHz, or 625MHz

- For 10GE optical: 20.14MHz, 40.28MHz, 80.56MHz, 161.13MHz,

322.26MHz, or 644.53MHz

Output frequency range selection

1x, 2x, 4x, 8x, 16x, and 32x outputs on QOUT

Regenerated input clock on QREG

Lock indicator

Power-down mode

LVPECL or LVDS outputs

Two modes of output frequency range

- Mode 0: QOUTrange 155.5 - 166.6MHz. QREG is a regenerated version

of the input clock.

- Mode 1: QOUT range 622 - 666.5MHz. QREG is a regenerated version

of the input clock frequency.

Hitless switchover

Differential LVPECL, LVDS, or single-ended LVTTL input interface

2.375 - 3.465V core and I/O

Available in VFQFPN package

use Replacement part: 8T49N222B-dddNLGI

DESCRIPTION:

The IDT5T929 generates a high precision FEC (Forward Error Cor-

rection) or non-FEC source clock for SONET/SDH systems as well as a

source clock for Gigabit Ethernet systems. This device also has clock

regeneration capability: it creates a "clean" version of the clock input by

using the internal oscillator to square the input clock's rising and falling

edges and remove jitter. In the event that the main clock input fails, the

device automatically locks to a backup reference clock using a hitless

switchover mechanism.

This device detects loss of valid CLKIN and leaves the VCO of the PLL at

the last valid frequency while an alternate input REFIN is selected. If CLKIN

andREFINaredifferentfrequencies,themultiplicationfactorwillbeadjustedto

retainthesameoutputfrequency.

TheIDT5T929canactasatranslatorfromadifferentialLVPECL,LVDS,or

single-ended LVTTL input to LVPECL or LVDS outputs. The IDT5T929-10

has LVDS outputs and the IDT5T929-30 has LVPECL outputs.

ThetwomodesofoutputfrequencyrangearecontrolledbytheSELmode.

WhenSELmodeishighorlow,theQOUTisamultipliedversionoftheinputclock

while QREG is a regenerated version of the input clock.

APPLICATIONS:

Terabit routers

Gigabit ethernet systems

SONET / SDH systems

Digital cross connects

Optical transceiver modules

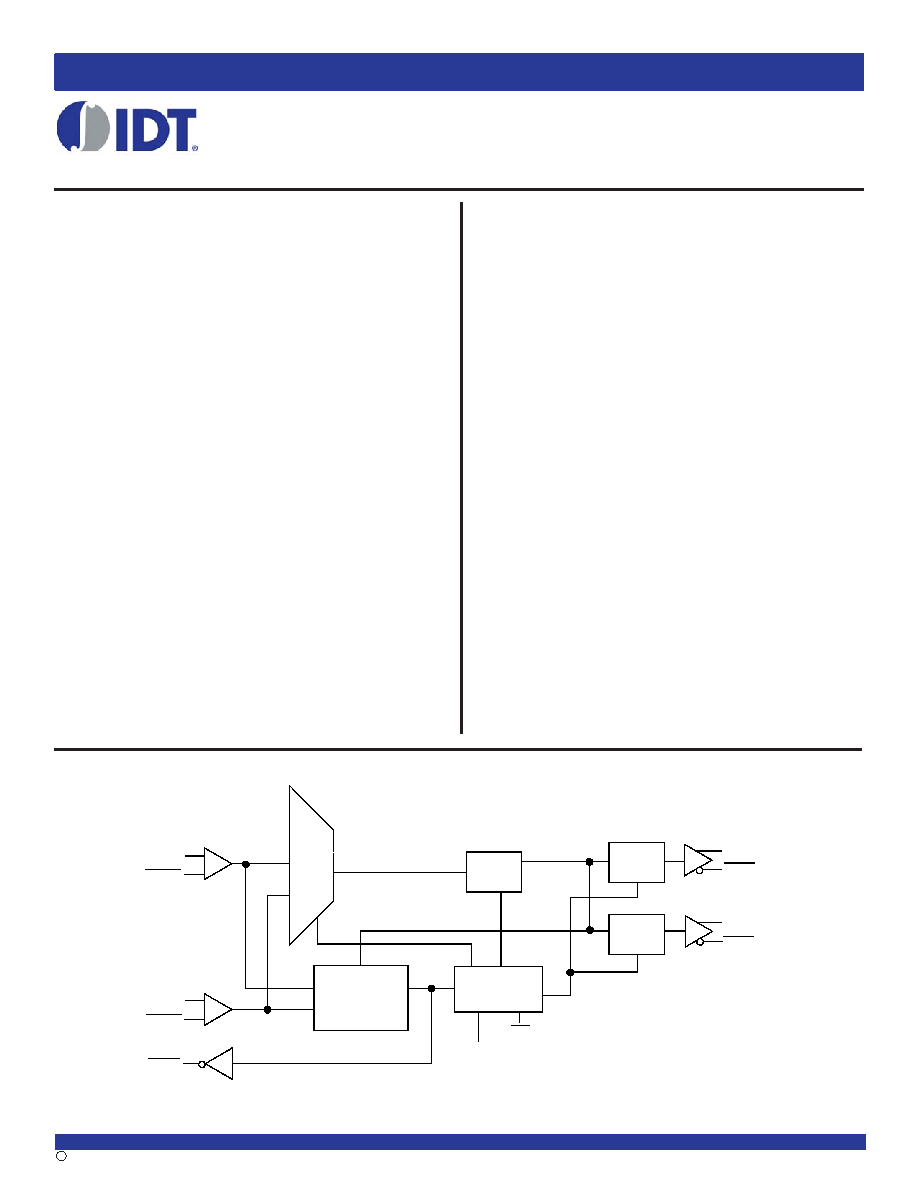

PLL

CONTROL

LOGIC

LOCK,

FREQ.

DETECTOR

CLKIN

REFIN

LOCK

DIVN

DIVM

QREG

QOUT

SELMODE

PD

INPUT

MUX

CLKIN

REFIN

QREG

QOUT

FUNCTIONAL BLOCK DIAGRAM

PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES ON OCTOBER 28, 2014

MAY 2013

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT5T940-10NLGI

IC CLK GENERATOR PREC 28-VFQFPN

IDT5T9820NLI8

IC CLK DRIVER ZD PLL 68-VFQFPN

IDT5T9890NLI8

IC CLK DRIVER 2.5V PLL 68-VFQFPN

IDT5V19EE604NDGI8

IC PLL CLK GEN 200MHZ 28VFQFPN

IDT5V40501DVG

IC CLK GEN PLL 160MHZ 8TSSOP

IDT5V41064NLGI

IC CLK GEN 1:1 16QFN

IDT5V41066PGG

IC CLK GEN SPRED SPECTRM 20TSSOP

IDT5V49EE901NLGI8

IC PLL CLK GEN 200MHZ 32VFQFN

相关代理商/技术参数

IDT5T929-30NLGI8

功能描述:IC CLOCK GENERATOR PREC 28VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT5T9302EJGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK BUFFER MUX 2:2 24-TSSOP

IDT5T9302EJGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK BUFFER MUX 2:2 24-TSSOP

IDT5T9302PGG

功能描述:IC CLOCK BUFFER MUX 2:2 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:TERABUFFER™ II 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件

IDT5T9302PGGI

功能描述:IC CLOCK BUFFER MUX 2:2 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:TERABUFFER™ II 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件

IDT5T9302PGGI8

功能描述:IC CLOCK BUFFER MUX 2:2 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:TERABUFFER™ II 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件

IDT5T9304EJGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK BUFFER MUX 2:4 24-TSSOP

IDT5T9304EJGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK BUFFER MUX 2:4 24-TSSOP